Тема: Триггер

Цель: использование логических устройств в вычислительной технике.

Повторение. Логические элементы.

Триггер (trigger – защелка, спусковой крючок) – это устройство позволяющее запоминать, хранить и считывать информацию.

Несколько триггеров (8, 16, 32, 64) объединяют вместе и получают устройство регистр.

Триггеры используются во всех вычислительных узлах компьютера – начиная с центрального процессора, оперативной памяти, в счетчиках, преобразователях последовательного кода в параллельный и.т.д.

Рассмотрим:

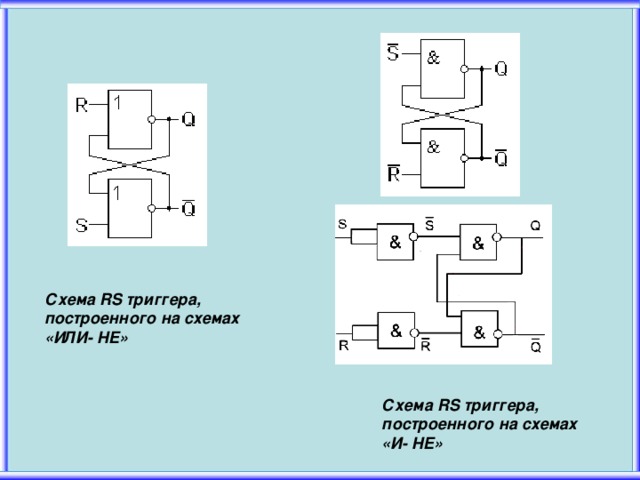

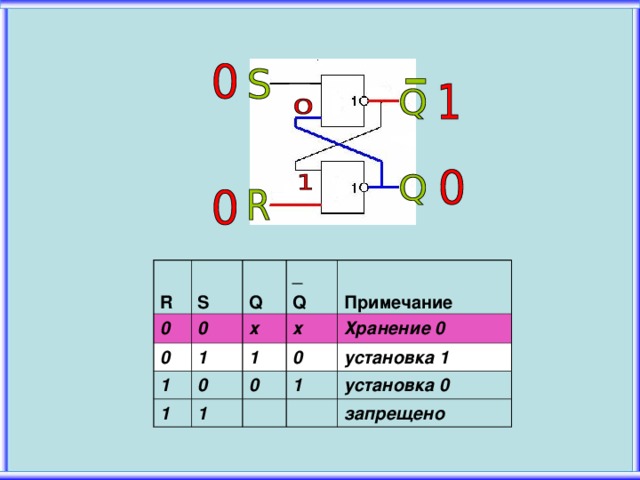

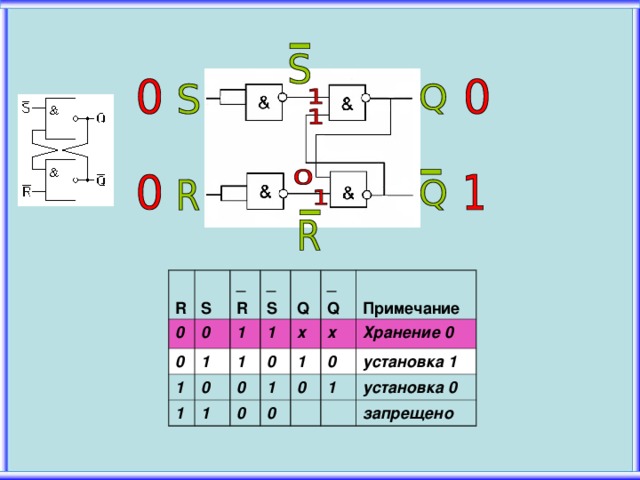

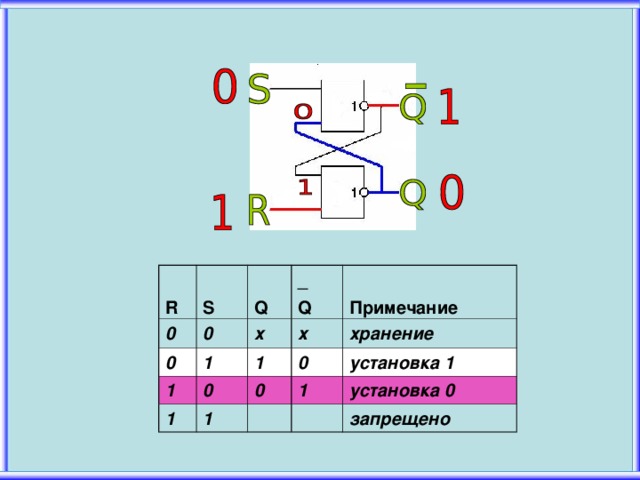

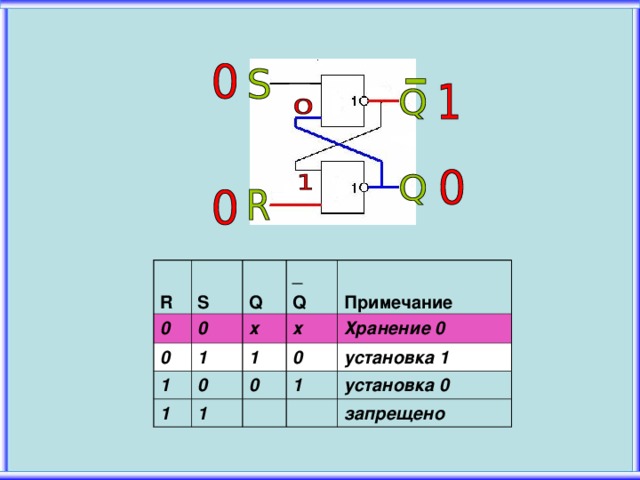

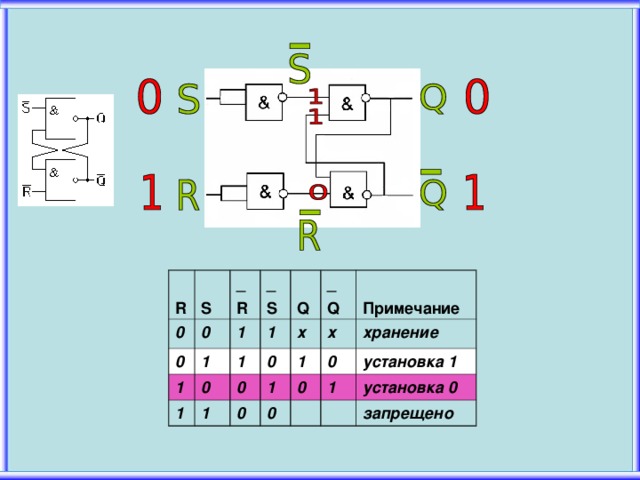

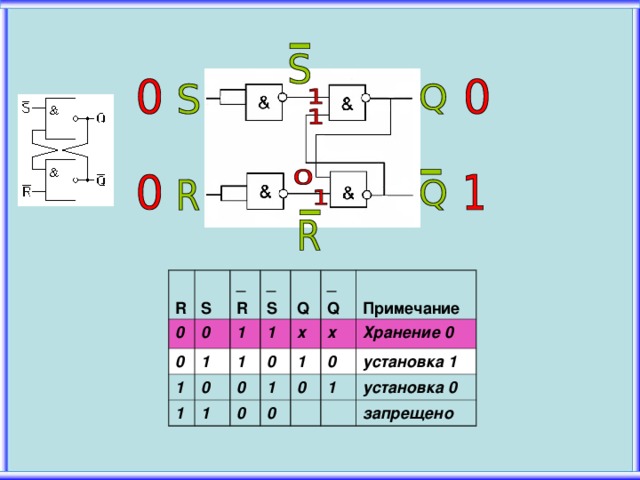

1. схему RS триггера, построенного на схемах «ИЛИ- НЕ»

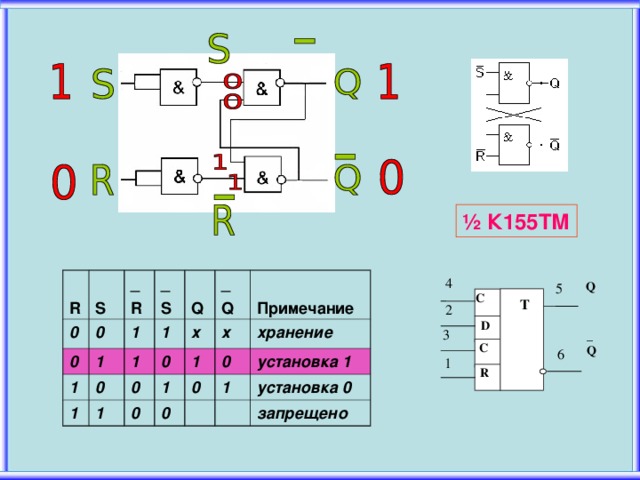

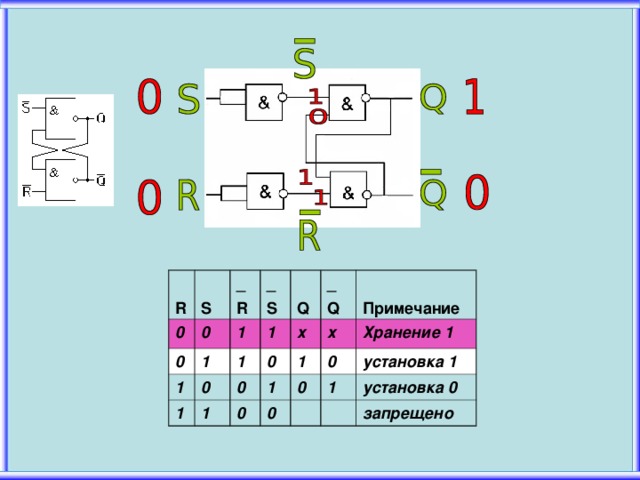

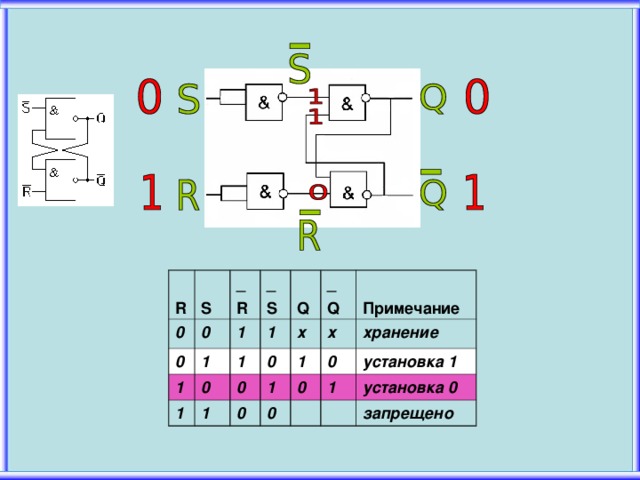

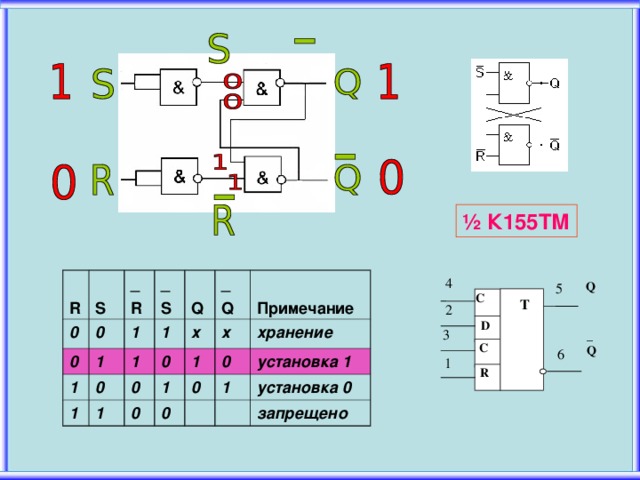

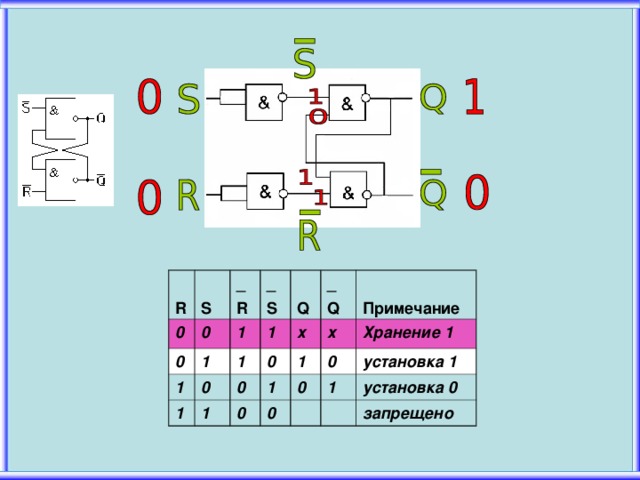

2. схему RS триггера, построенного на схемах «И- НЕ»

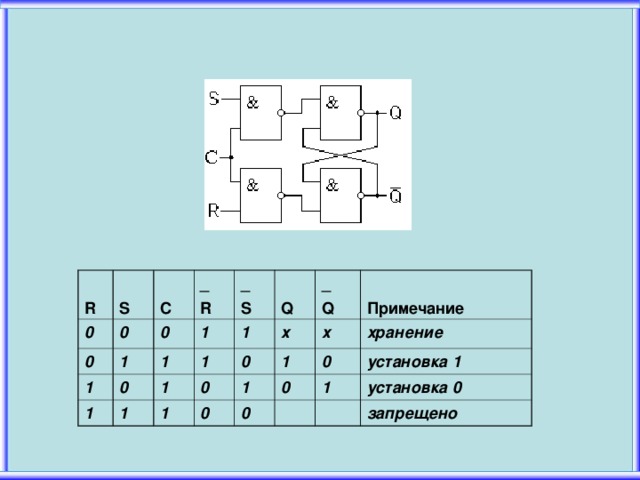

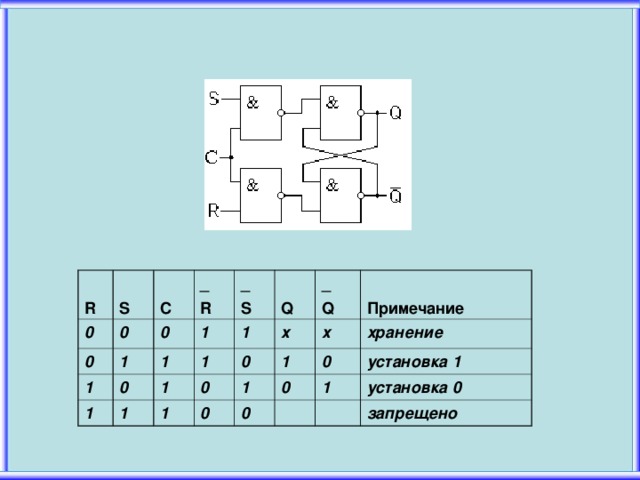

При изменении входных сигналов возникает переходной процесс («опасные гонки»), поэтому запоминать состояния логической схемы нужно только в определенные моменты времени, когда все переходные процессы закончены, т.е требуется сигнал синхронизации (тактовый сигнал).

Все переходные процессы в логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггера. Приведена схема синхронного на двух «И - НЕ» RS - триггера.

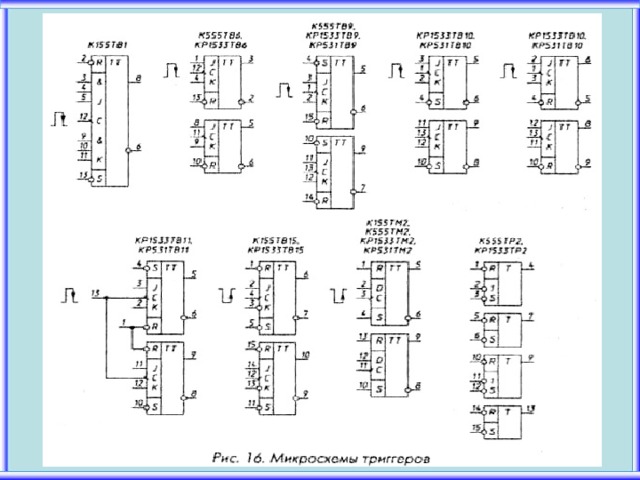

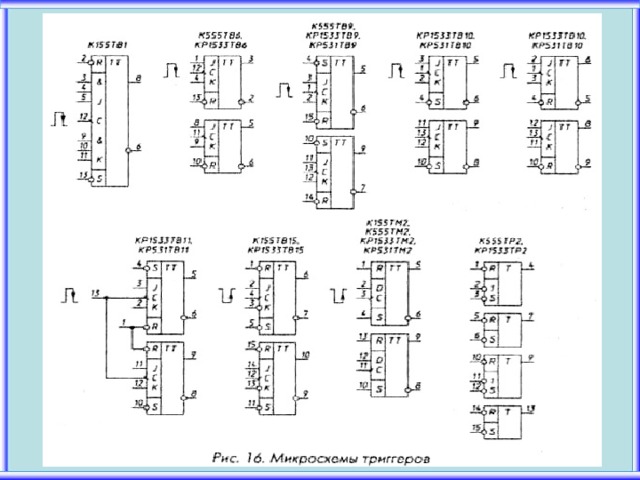

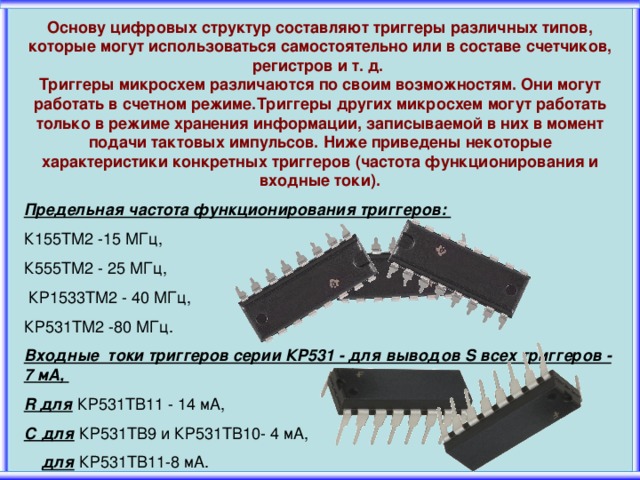

Основу цифровых структур составляют триггеры различных типов, которые могут использоваться самостоятельно или в составе счетчиков, регистров и т. д.

Триггеры микросхем различаются по своим возможностям. Они могут работать в счетном режиме. Триггеры других микросхем могут работать только в режиме хранения информации, записываемой в них в момент подачи тактовых импульсов. Ниже приведены некоторые характеристики конкретных триггеров (частота функционирования и входные токи).

Предельная частота функционирования триггеров:

К155ТМ2 -15 МГц,

К555ТМ2 - 25 МГц,

КР1533ТМ2 - 40 МГц,

КР531ТМ2 -80 МГц.

Входные токи триггеров серии КР531 - для выводов S всех триггеров - 7 мА,

R для КР531ТВ11 - 14 мА,

С для КР531ТВ9 и КР531ТВ10- 4 мА,

для КР531ТВ11-8 мА.

Просмотр содержимого презентации

«trigger»

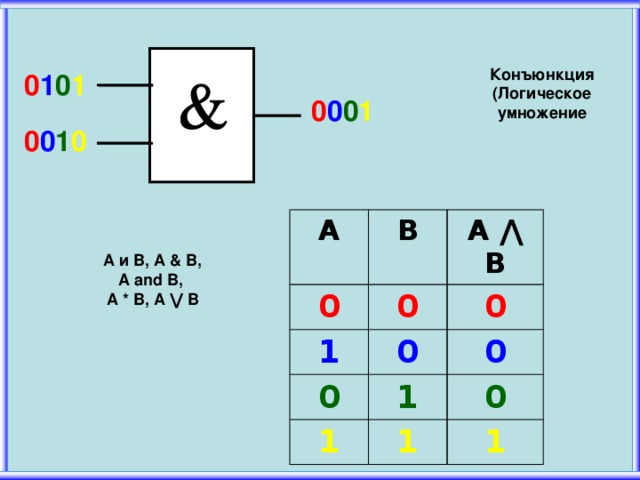

0 1 0 1

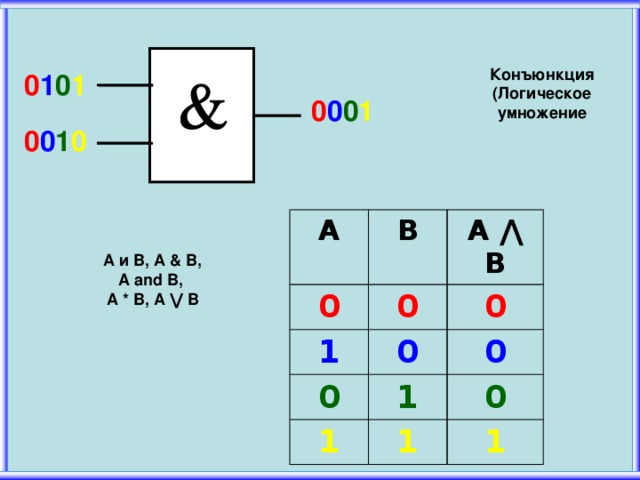

Конъюнкция

(Логическое

умножение

0 0 0 1

0 0 1 0

А

0

В

1

A ⋀ B

0

0

0

0

1

1

0

1

0

1

А и В, А & В,

A and B,

A * B, A ⋁ B

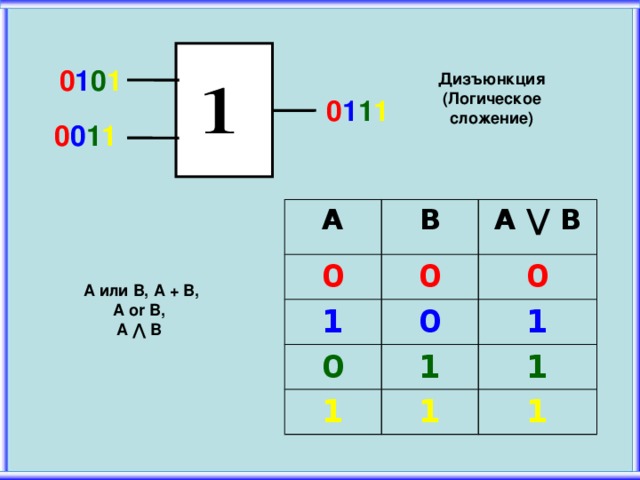

0 1 0 1

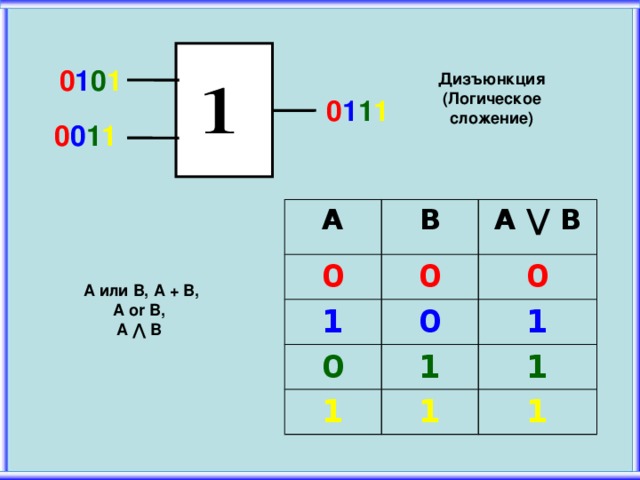

Дизъюнкция

(Логическое

сложение)

0 1 1 1

0 0 1 1

А

В

0

0

1

A ⋁ B

0

0

0

1

1

1

1

1

1

А или В, А + В,

A or B,

A ⋀ B

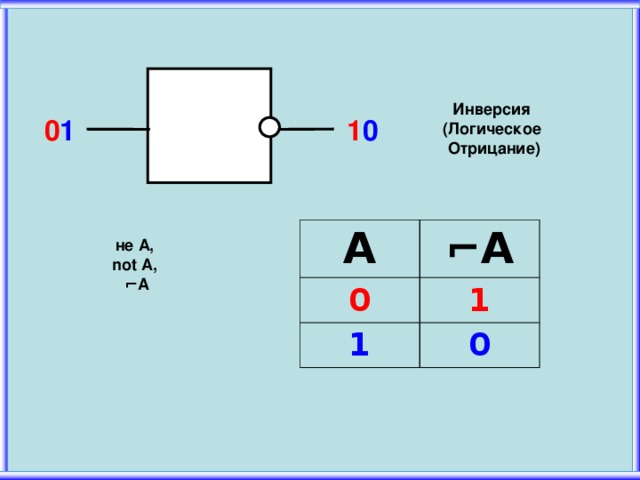

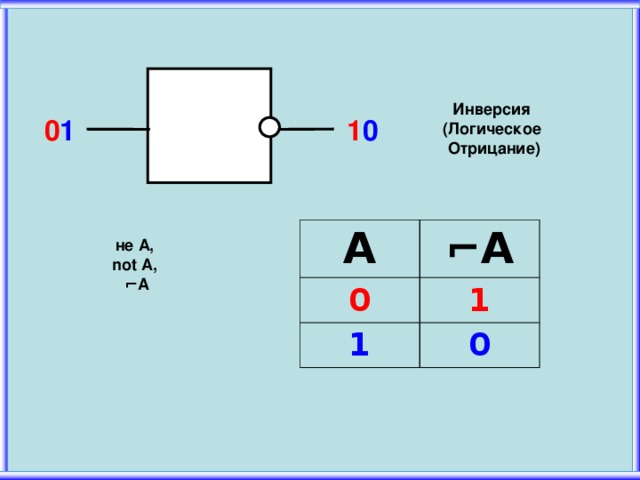

Инверсия

(Логическое

Отрицание)

0 1

1 0

А

0

⌐ A

1

1

0

не А,

not A,

⌐ A

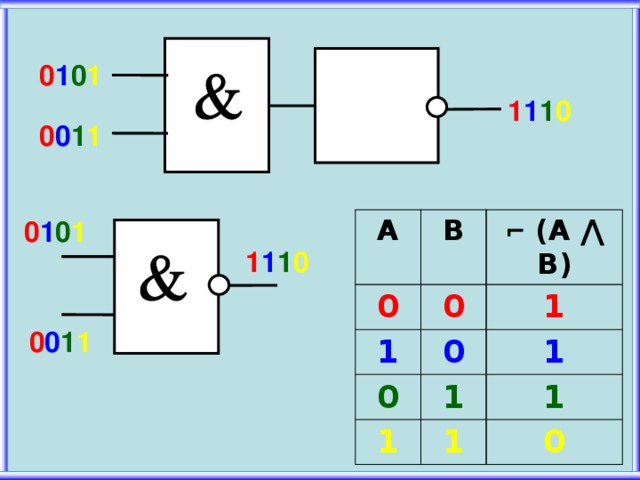

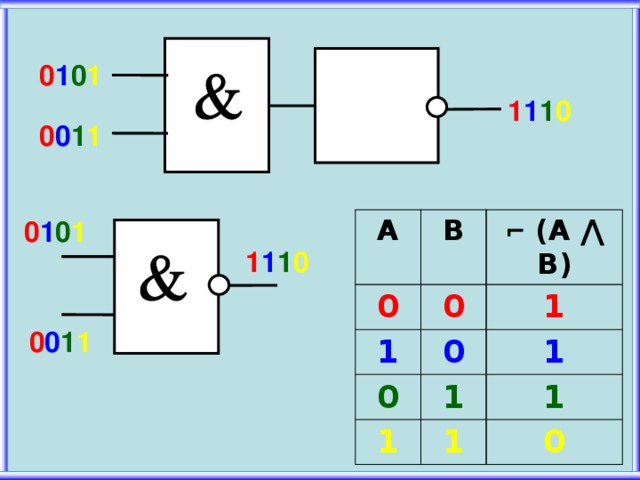

0 1 0 1

1 1 1 0

0 0 1 1

0 1 0 1

А

0

В

⌐ (A ⋀ B)

0

1

1

0

0

1

1

1

1

1

0

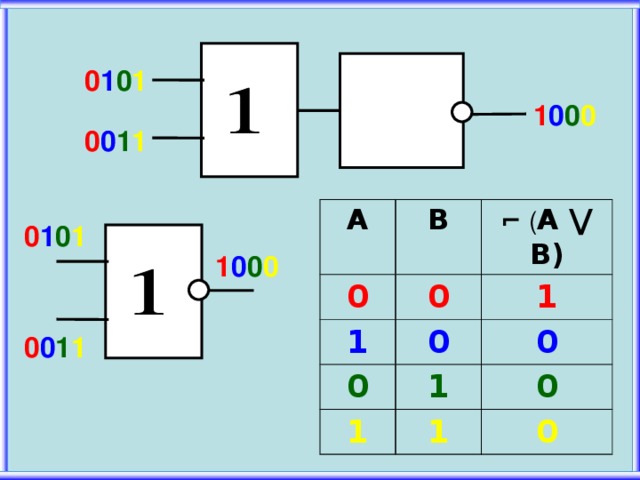

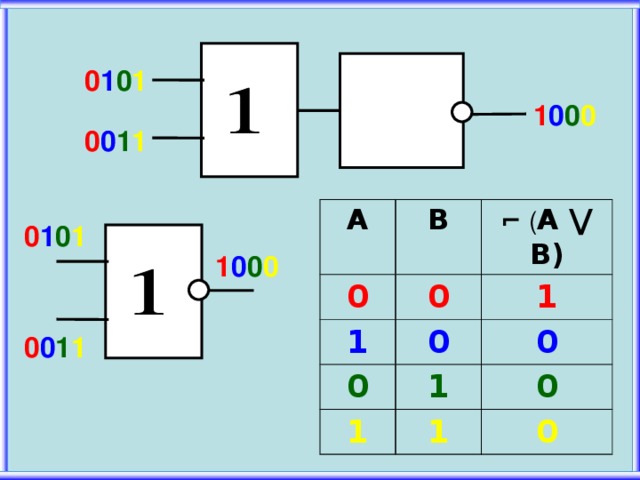

1 1 1 0

0 0 1 1

0 1 0 1

1 0 0 0

0 0 1 1

А

В

0

⌐ ( A ⋁ B)

1

0

0

0

1

1

1

0

1

0

0

0 1 0 1

1 0 0 0

0 0 1 1

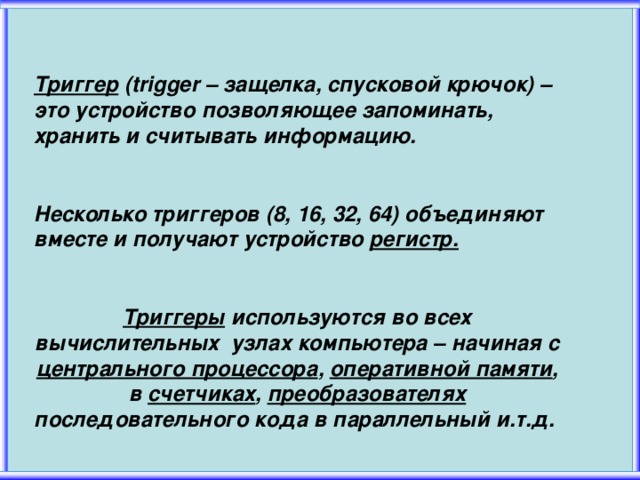

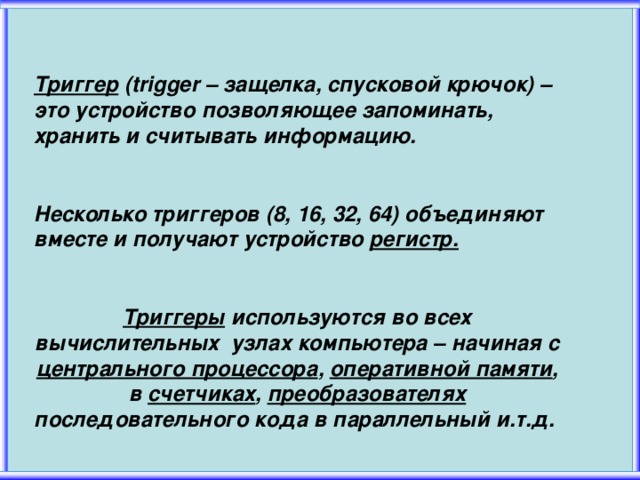

Триггер ( trigger – защелка, спусковой крючок) – это устройство позволяющее запоминать, хранить и считывать информацию.

Несколько триггеров (8, 16, 32, 64) объединяют вместе и получают устройство регистр.

Триггеры используются во всех вычислительных узлах компьютера – начиная с центрального процессора , оперативной памяти , в счетчиках , преобразователях последовательного кода в параллельный и.т.д.

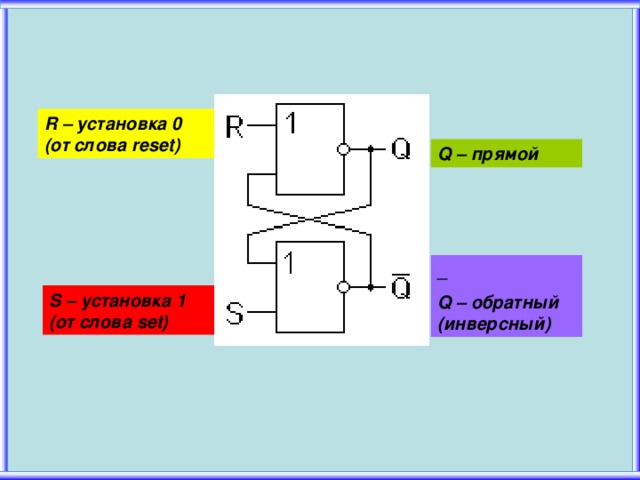

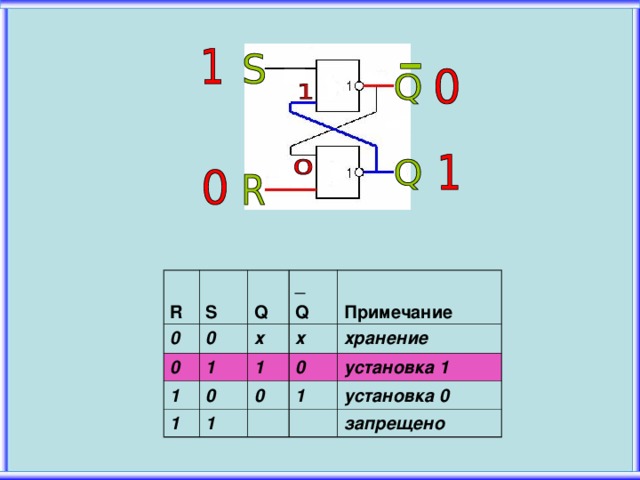

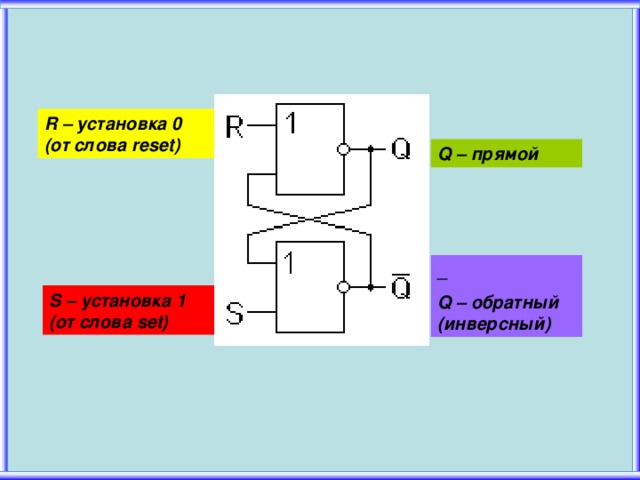

R – установка 0 (от слова reset)

Q – прямой

_

Q – обратный (инверсный)

S – установка 1 (от слова set)

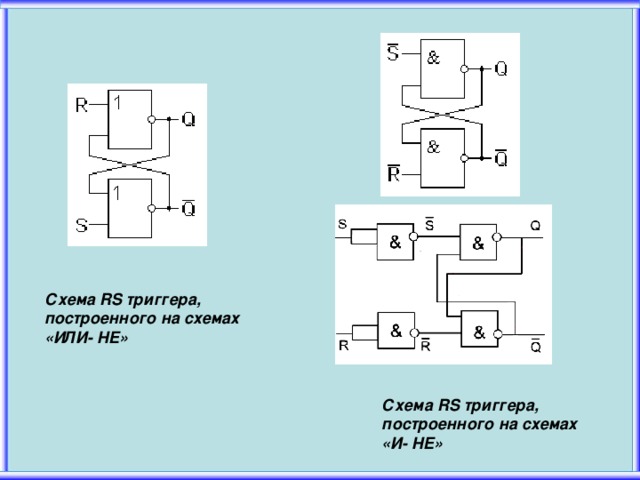

Схема RS триггера, построенного на схемах «ИЛИ- НЕ»

Схема RS триггера, построенного на схемах «И- НЕ»

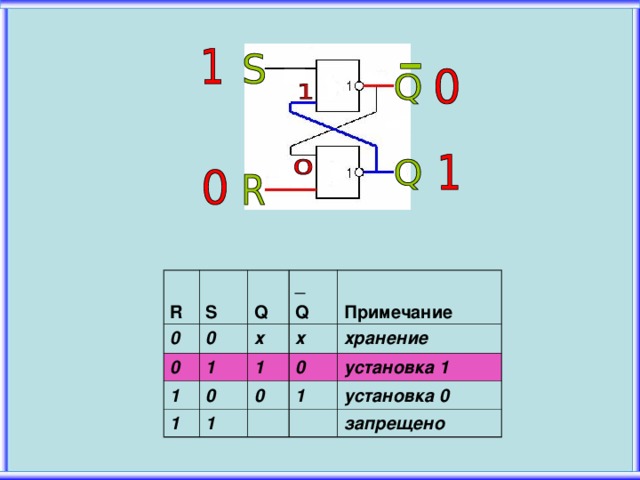

R

0

S

0

Q

0

1

1

_

Q

х

Примечание

х

1

1

0

хранение

0

0

1

установка 1

1

установка 0

запрещено

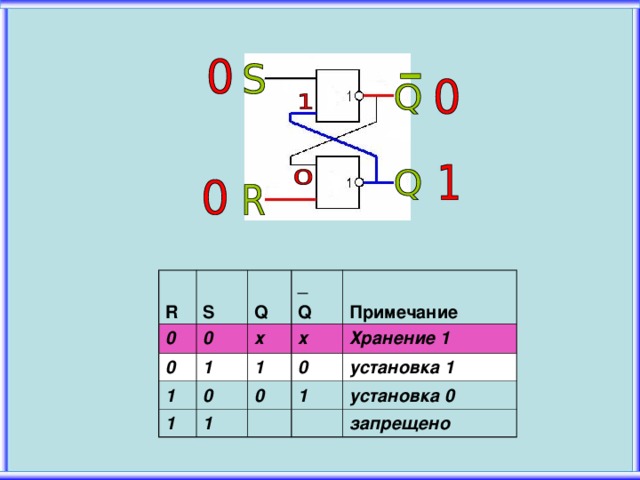

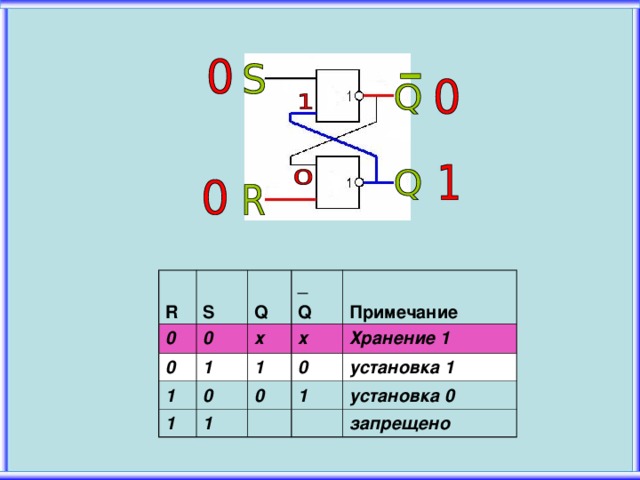

R

0

S

0

Q

0

1

1

_

Q

х

Примечание

х

1

1

0

Хранение 1

0

0

1

установка 1

1

установка 0

запрещено

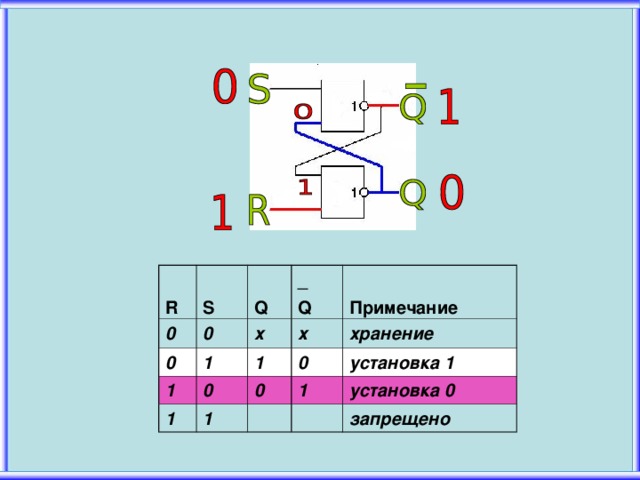

R

0

S

0

Q

0

1

1

_

Q

х

Примечание

х

1

1

0

хранение

0

0

1

установка 1

1

установка 0

запрещено

R

0

S

0

Q

0

1

1

_

Q

х

Примечание

х

1

1

0

Хранение 0

0

0

1

установка 1

1

установка 0

запрещено

½ К155ТМ

4

R

0

S

0

_

R

0

_

S

1

1

1

1

1

Q

0

1

х

0

1

_

Q

0

0

1

Примечание

х

1

0

0

хранение

0

установка 1

1

установка 0

запрещено

Q

5

C

T

2

D

3

_

Q

C

6

1

R

R

0

S

0

0

_

R

1

_

S

1

1

1

1

Q

0

1

х

0

_

Q

0

1

х

0

Примечание

1

1

0

Хранение 1

0

0

установка 1

1

установка 0

запрещено

R

0

S

0

_

R

0

1

1

_

S

1

Q

1

1

1

0

х

0

_

Q

0

1

0

1

1

х

Примечание

0

хранение

0

0

1

установка 1

установка 0

запрещено

R

0

S

_

R

0

0

1

1

_

S

1

1

1

Q

1

0

х

0

_

Q

0

1

0

1

х

1

Примечание

0

0

Хранение 0

0

1

установка 1

установка 0

запрещено

сигнал синхронизации

При изменении входных сигналов возникает переходной процесс (« опасные гонки »), поэтому запоминать состояния логической схемы нужно только в определенные моменты времени, когда все переходные процессы закончены, т.е требуется сигнал синхронизации (тактовый сигнал).

Все переходные процессы в логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггера. Схема синхронного на двух «И - НЕ» RS - триггера приведена на рисунке.

R

S

0

0

C

0

_

R

1

0

1

_

S

1

0

1

1

1

1

1

1

Q

0

1

_

Q

0

х

1

0

Примечание

х

1

0

0

хранение

0

1

установка 1

установка 0

запрещено

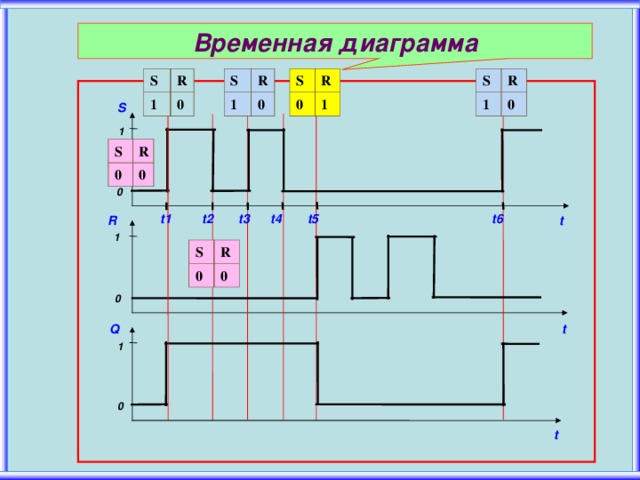

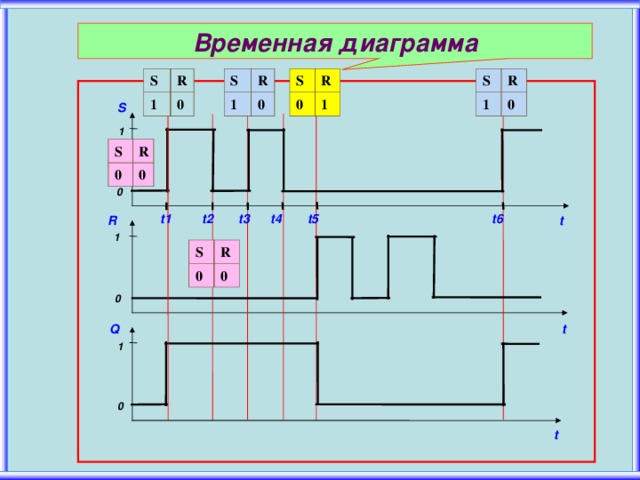

Временная диаграмма

S

S

S

S

R

1

R

1

0

R

1

R

0

1

0

0

S

1

S

0

R

0

0

t6

t5

t1

t2

t3

t4

R

t

1

S

0

R

0

0

Q

t

1

0

t

Основу цифровых структур составляют триггеры различных типов, которые могут использоваться самостоятельно или в составе счетчиков, регистров и т. д.

Триггеры микросхем различаются по своим возможностям. Они могут работать в счетном режиме . Триггеры других микросхем могут работать только в режиме хранения информации, записываемой в них в момент подачи тактовых импульсов. Ниже приведены некоторые характеристики конкретных триггеров (частота функционирования и входные токи).

Предельная частота функционирования триггеров:

К155ТМ2 -15 МГц,

К555ТМ2 - 25 МГц,

КР1533ТМ2 - 40 МГц,

КР531ТМ2 -80 МГц.

Входные токи триггеров серии КР531 - для выводов S всех триггеров - 7 мА,

R для КР531ТВ11 - 14 мА,

С для КР531ТВ9 и КР531ТВ10- 4 мА,

для КР531ТВ11-8 мА.

Домашнее задание.

1. Н. Угринович. Информатика и информационные технологии М. ЛБЗ 2007г. П 3.7.3. С.144-145. Выполнить задание 3.10. С. 145.

2. А. Г. Кушниренко и др. Основы информатики и вычислительной техники. М. Просвещение 1995г. П. 18 С.146-154.